FM 라디오 회로도인데, 초간단 설명 부탁드립니다!

2010.11.01 19:08

[질문 수정합니다]

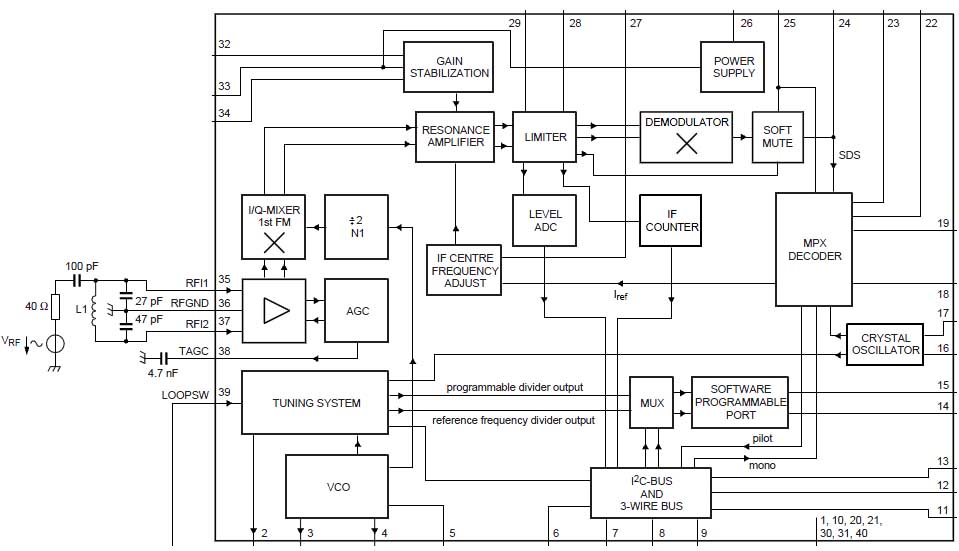

FM 라디오 기능블록도입니다.

RF가 수신되어서 처리되는 순서를 보면

안테나 -> LNA -> AGC -> 믹서&국부발진기 -> 증폭기 -> 필터 -> 디모듈레이터 -> MPX 디코더의 순서인 것 같습니다.

MPX 디코더에서 베이스밴드로 변조해서 MPX 포맷의 신호를 출력함으로써 FM 수신의 전 과정이 처리되는 것 같구요.

IF 카운터와 레벨 ADC는 주파수 / 채널 selection이 제대로 되었는지 확인하여 VCO를 제어하는 기능을 하는 것 같습니다. (그럼, 이게 PLL -phase lock loop 인거죠? IF 카운터는 PLL의 디바이더-분주기구요.)

그렇다면, 이건 그냥 아날로그 방식이 되어버린단 말이죠.

아래 케퍽의 유령님 답변 달아주신 것처럼...리미터와 디모듈레이터 사이에 ADC가 있어야 할 것 같은데 말입니다.

음...

코멘트 8

-

왕초보

11.02 00:28

뭐하시게요 ? 개념도에서 아날록/디지탈을 구별해 줄 필요는 없지요.

-

근데 MPX decoder는 스테레오 분리를 하는 부분입니다. 수신 절차는 demodulator에서 이미 끝난거고 MPX를 거치면 스테레오 아날로그 신호가 됩니다.

-

Demodulator 이후 부분을 아날로그로 구현 하는것도 가능 하니까, 반드시 ADC 가 있어야 하는것은 아니겠죠.

특정 IC 의 아키텍쳐를 질문하시는 건가요?? 그럼 해당 IC 의 datasheet 을 보시면 좀 더 자세한 설명이 나올텐데요..

-

그리고 Level ADC 는 Signal Level meter용 ADC로 보입니다. 앞에 수정 전 질문을 자세히 안봤는데 위의 블록 다이어그램에서 디지털 도메인과 아날로그 도메인을 구분하는게 목적이신가요?

제가 보기엔 위 구조에서 DSP로 구현 가능한 것은 demodulator 인듯 합니다. 그리고 demodulator에서 나오는 신호는 별도의 MPX가 붙는걸로 보아 아날로그 아닐까요? 아니면 MPX를 분리했을리가..

(솔직히 잘 모르겠습니다. -_-a...)

-

아콰필님 하시는 일로 짐작해볼때 기존의 FM 수신 칩과 다른 방식의 칩일것 같은데요?

근데 디지털 FM receiver IC의 블럭다이어그램을 보면 수신부만 아날로그고 일단 수신 한 다음에 바로 ADC 해서 위와 같은 블럭들의 뒷부분을 통째로 DSP로 처리하고 오디오 출럭도 디지털로 내보내던데요..

-

아무리봐도 위의 칩은 아날로그 칩인것 같은데요.. -_-a...

솔직히 잘 모르겠습니다...(2)

-

모사야

11.03 00:23

그냥 PLL 내장형 아날로그 튜너 IC 회로 입니다. 위 블럭에서 ADC 는 전계 강도(일반적으로 RSSI 또는 S-meter Level 이라고 합니다.) 를 I2C 로 읽어 내기 위해 있고요, 자동으로 방송국 찾아 주는 기능구현 (라디오에서 Seek 기능) 을 위해서 1차로 체크하는 부분이 전계 강도 이고요, 그다음에 대충 방송이 있는거 같으면 정말 방송이 있는지 없는지 확인 하기 위해 IF 주파수 카운팅을 합니다.

그래서 IF 값도 I2C 로 읽어 낼수 있게 블럭이 구현되어 있고요,

무슨 목적이신지 모르겠지만 일반적으로 위 블럭에서 limiter 단 대신에 DSP 가 이후 모든 과정을 처리하는 경우

디지털 튜너라고 부릅니다. 그리고 사족일런지 모르겠지만 limiter 단에 어떤 dsp 가 붙느냐에 따라서 일반 FM 방송이 아닌

미국향 HD 라디오 구현도 가능하며 일반적으로 판매(?) 하고 있는 DIF 튜너의 경우 위 기능을 지원합니다.

저도 땜쟁이 전공이긴 한데... 분야가 좀 달라서리..

Block diagram 상으로 볼 때는 전체가 analog 로 되어 있는것 처럼 보이기는 하는데...

그림상에서 Limiter 다음에 ADC 가 있는데, 이것을 생략하고 그렸는지도 (즉 demodulator 부터가 DSP )모르겠네요..